## **INTERVENTO DEL MESE**

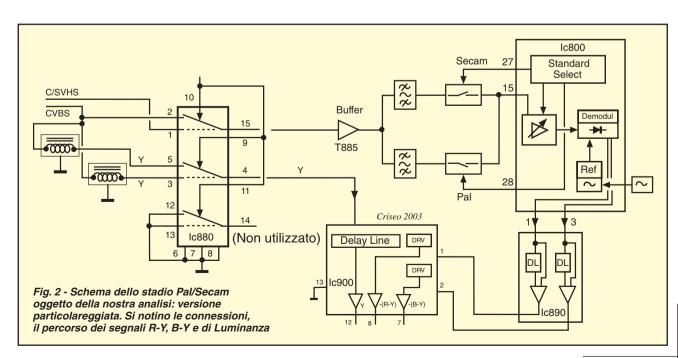

Fig. 1 - Sezione decodifica Pal/Secam. Si noti la presenza dei commutatori di standard T805 e T855

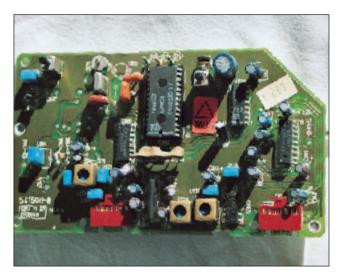

Foto 4 - Lato componenti del Modulo Croma Pal/Secam

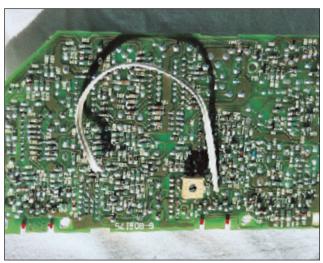

Foto 5 - Lato saldature della Sezione Decoder che equipaggia questo TVC

in fase fra loro è necessario che la classica linea di ritardo agisca sul segnale di Luminanza.

Questa linea di ritardo si ottiene tramite un registro a scorrimento del tipo FIFO, circuito elettronico capace di trasmettere in uscita un bit d'ingresso dopo un certo numero di campionamenti.

Appare evidente che, maggiore è il numero di registri posti in cascata, maggiore sarà il numero di campionamenti necessari affinché un determinato bit in ingresso arrivi in uscita (ovvero sull'ultimo registro presente nella cascata).

Per comprendere meglio quanto detto si veda la **Fig. 3**.

Il segnale analogico sarà prima convertito in digitale, successivamente verrà ritardato del tempo Dt considerato. Alla fine, avremo una riconversione in analogico e l'invio all'esterno attraverso il pin 12.

A questo proposito è possibile imporre un tempo di ritardo che

va da un minimo di 670 ns a un massimo di 1060 ns.

Il tempo totale di ritardo lo si impone dal partitore resistivo dato da R902, R901.

Dai valori nello schema elettrico e considerando che la corrente assorbita entro il pin 15 del chip non supera mai i 20 μA ÷ 25 μA, possiamo considerare (se pur in prima approssimazione) nulla tale corrente, ottenendo una tensione di polarizzazione sul pin 15 pari a: